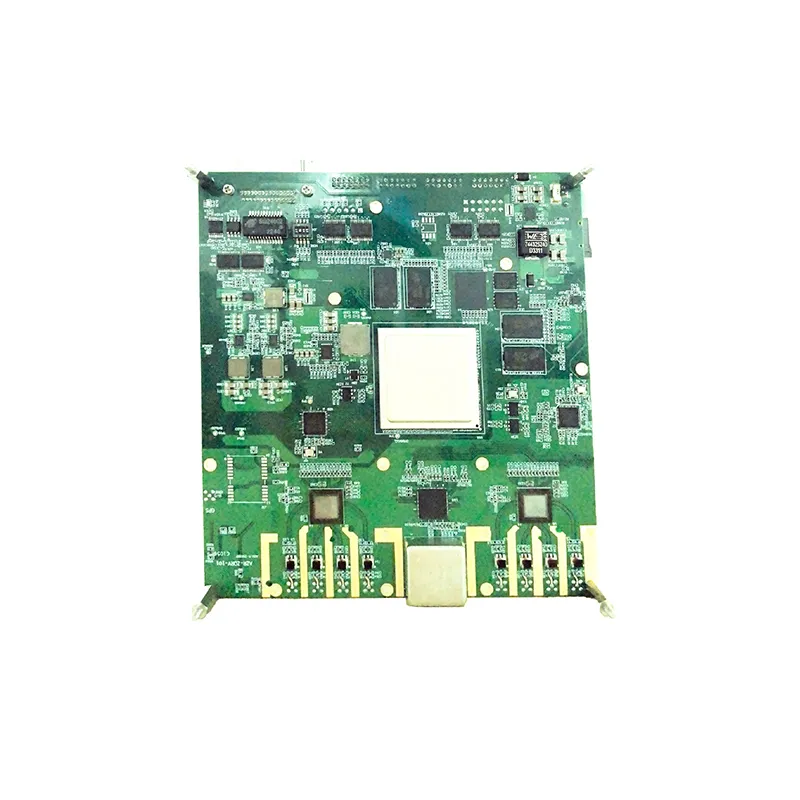

Цифровая процессорная плата производитель

Когда слышишь ?цифровая процессорная плата производитель?, многие сразу думают о готовых модулях под ключ. Но на деле это часто путь от прототипа до серии, где каждая итерация — это борьба с синхронизацией тактовых генераторов или подавлением ЭМП. Мы в ООО Чэнду Битэ Чжиань Технологии через это прошли — особенно когда делали платы для систем синхронизации времени.

Ошибки проектирования и реалии производства

Помню, как в 2021 году мы запустили плату для магистральных устройств синхронизации. Расчеты в CAD были идеальны, но на тестах дрожал PLL — оказалось, проблема в разводке земли под BGA-корпусом процессора. Пришлось перекладывать четыре слоя, и это задержало выход на месяц.

Часто производители цифровых плат недооценивают требования к стабильности частоты. В системах, где синхронизация критична (например, для наших оконечных устройств), даже 5 ppm могут вызвать рассинхронизацию в сети. Мы тестируем каждую партию кварцевых генераторов в термокамере — не потому что так надо по ТЗ, а потому что на третьей партии были срывы при -40°C.

Еще один нюанс — выбор компонентов. Российские заказчики часто требуют импортозамещения, но с цифровыми процессорными платами это сложно: отечественные АЦП пока отстают по jitter. Приходится искать гибридные решения, где процессор импортный, а обвязка — локальная.

Связь с нелетальным оборудованием: неочевидные кейсы

Наш сайт https://www.cdbtzakj.ru описывает нас как поставщика нелетального оборудования, но мало кто знает, что те же процессорные платы идут в блоки управления электронными контрмерами. Например, в системе подавления БПЛА мы используем плату на базе Xilinx Zynq — она обрабатывает сигналы с двух каналов и управляет излучателем.

Здесь важна не только вычислительная мощность, но и энергоэффективность. В полевых условиях плата питается от аккумуляторов, и мы долго подбирали DC/DC-преобразователи, чтобы снизить тепловыделение. В итоге применили импульсные стабилизаторы с КПД 94% — это дало +2 часа работы.

Интересно, что для низковысотных систем защиты мы сначала пробовали универсальные процессорные платы, но столкнулись с задержками обработки данных. Пришлось разрабатывать кастомный вариант с FPGA, где часть алгоритмов работает на аппаратном уровне. Это снизило latency до 3 мс — критично для обнаружения целей.

Процессорные платы в синхронизации времени: детали, которые не пишут в спецификациях

Когда мы начали производство магистральных устройств синхронизации, то думали, что главное — точность часов. Оказалось, что цифровая процессорная плата влияет на стабильность сигнала через джиттер тактовых генераторов. Мы перебрали три типа генераторов TCXO, пока не нашли вариант с температурным дрейфом менее ±0.1 ppm.

Еще один момент — интерфейсы. Современные системы требуют не только PTP, но и резервные каналы типа IRIG-B. Мы разместили на плате два физических порта, но пришлось экранировать их от цифровых линий, чтобы избежать наводок. Это увеличило стоимость, но без этого в промышленных условиях были сбои.

Сейчас мы тестируем плату для оконечных устройств с поддержкой White Rabbit. Протокол сложный, и на отладку ушло полгода — особенно трудно было добиться точности ниже 1 нс. Думаю, если бы мы изначально заложили более мощный процессор, сроки были бы короче.

Проблемы совместимости и как мы их обходим

В интеллектуальном оборудовании для электронных контрмер часто используются специализированные шины данных. Наша процессорная плата должна работать с устаревшими интерфейсами (например, MIL-STD-1553), и это создает сложности при разводке. Мы добавили буферные микросхемы, но пришлось жертвовать площадью платы.

С программной частью тоже не все гладко. Для российского рынка мы пишем драйверы под ОС РВ, и иногда обнаруживаем, что прерывания обрабатываются с задержкой. В таких случаях помогает тонкая настройка DMA-контроллера — но это уже уровень ассемблера, и не каждый инженер справится.

Недавно был случай: заказчик жаловался на сбои при работе в условиях ВЧ-помех. Оказалось, что проблема не в процессоре, а в разъеме питания — он недостаточно экранирован. Заменили на вариант с металлическим кожухом, и помехи исчезли. Мелочь, а влияет.

Эволюция подходов к производству

Раньше мы делали платы по принципу ?работает — и хорошо?. Теперь каждый этап проверяем: от импеданс-контроля дорожек до термоциклирования. Например, для процессорных плат в системах синхронизации мы ввели обязательный тест на старение — платы работают 72 часа при максимальной нагрузке, и только потом идут на сборку.

С компонентами тоже стало строже. После санкций некоторые микросхемы исчезли с рынка, и мы перешли на аналоги от азиатских производителей. Но тут своя головная боль: партии могут отличаться по параметрам, и приходится тестировать каждую.

Сейчас экспериментируем с платами на базе RISC-V. Архитектура перспективная, но инструменты отладки сырые. Если удастся наладить, это даст нам независимость от зарубежных поставщиков. Пока что прототип показывает скорость до 500 МГц — для наших задач маловато, но для простых контрмер хватит.

Заключительные мысли: куда движется отрасль

Если говорить о трендах, то цифровые процессорные платы становятся более специализированными. Универсальные решения уступают место кастомным разработкам — особенно в области защиты и электронных контрмер. Мы в ООО BISEC Технологии видим это по запросам клиентов: им нужны не просто платы, а готовые модули с предустановленным ПО.

Еще один момент — безопасность. Раньше мало кто задумывался о защите прошивки, но теперь даже для нелетального оборудования требуют криптографическую аутентификацию. Мы добавляем в платы TrustZone-совместимые чипы, но это усложняет схему и повышает цену.

В целом, производство процессорных плат — это всегда компромисс между стоимостью, надежностью и сроками. Мы научились находить баланс, но каждый новый проект — это снова риски и поиски. Главное — не бояться переделывать, если что-то пошло не так. Как в том случае с разводкой под BGA — тогда мы потеряли время, но зато теперь знаем, как избежать подобных ошибок.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

Мобильная система контроля воздушного пространства от БПЛА UDKS-OBU

Мобильная система контроля воздушного пространства от БПЛА UDKS-OBU -

Плата обнаружения и подавления

Плата обнаружения и подавления -

Комплекс разведки и противодействия БПЛА LG-ADH1601

Комплекс разведки и противодействия БПЛА LG-ADH1601 -

«Линцзю» (Гриф) LG-ADH1604

«Линцзю» (Гриф) LG-ADH1604 -

BL-ADH1302 Оборудование нейтрализации БПЛА

BL-ADH1302 Оборудование нейтрализации БПЛА -

BL-ADH1301 Оборудование нейтрализации БПЛА

BL-ADH1301 Оборудование нейтрализации БПЛА -

BL-ADH1402 Оборудование разведки и подавления БПЛА

BL-ADH1402 Оборудование разведки и подавления БПЛА -

Комплекс разведки и противодействия БПЛА «Кулик»

Комплекс разведки и противодействия БПЛА «Кулик» -

BL-ADG1000 Оборудование противодействия навигации БПЛА

BL-ADG1000 Оборудование противодействия навигации БПЛА -

BL-ADH1401 Оборудование разведки и подавления БПЛА

BL-ADH1401 Оборудование разведки и подавления БПЛА -

BL-ADH2601 Оборудование разведки и нейтрализации БПЛА

BL-ADH2601 Оборудование разведки и нейтрализации БПЛА -

«Бастион» BL-ADG2001

«Бастион» BL-ADG2001

Связанный поиск

Связанный поиск- Радиоэлектронное противодействие бпла основный покупатель

- Китай станция подавления бпла капюшон

- Детектор обнаружения беспилотных авиационных систем основный покупатель

- Китай лазерные системы обнаружения

- Обнаружение и подавление бпла производитель

- Комплекс обнаружения бпла зонтик основный покупатель

- Бпла антитеррора и борьбы с наркомафией

- Китай мобильное противодействие бпла

- Китай система обнаружения малоразмерных, низколетящих и медленных целей (мнмц)

- Многодиапазонное оборудование помех связи бпла