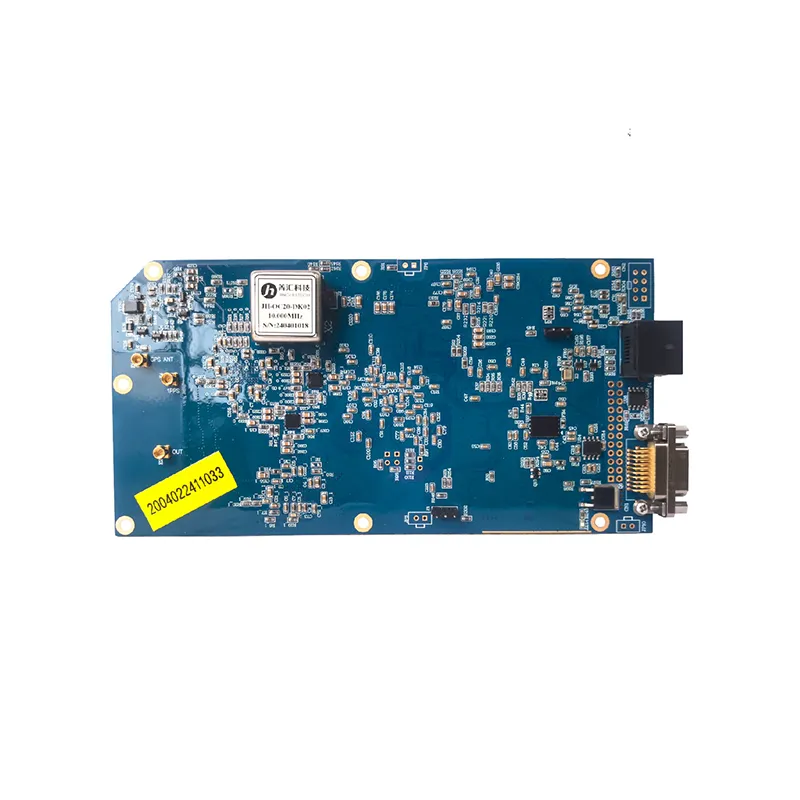

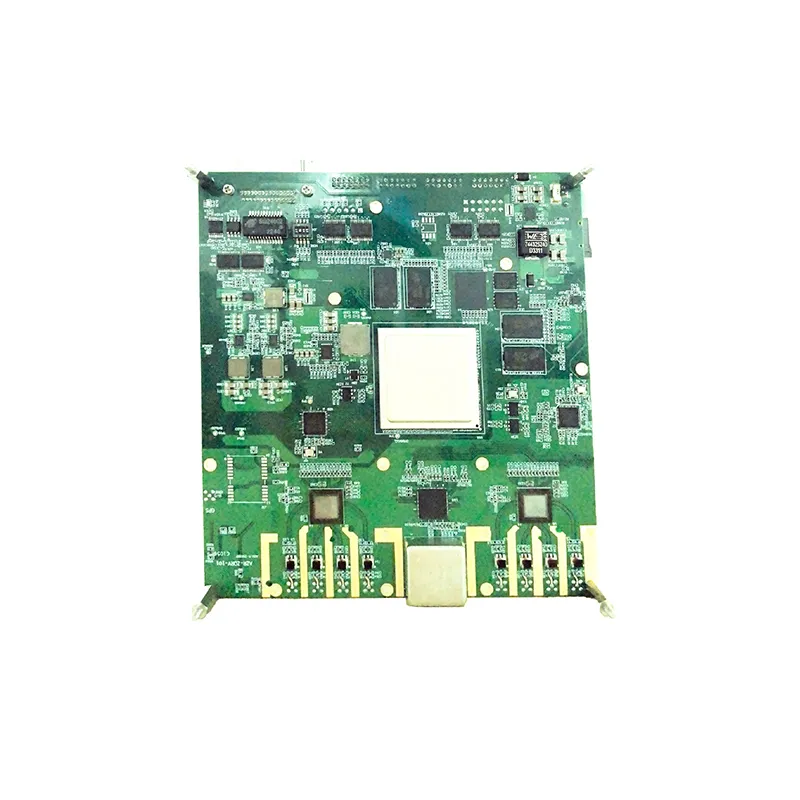

Цифровая процессорная плата

Когда слышишь 'цифровая процессорная плата', первое, что приходит в голову — универсальный вычислительный модуль. Но в нише низковысотной защиты это скорее специализированный контроллер, жёстко заточенный под обработку сигналов в реальном времени. Многие ошибочно полагают, что достаточно взять готовую FPGA-плату — и система заработает. На практике же...

Эволюция архитектуры плат в нелетальных системах

В 2018-м мы столкнулись с курьёзным случаем: заказчик принёс плату на Xilinx Kintex-7, купленную у стороннего поставщика. Технические характеристики впечатляли — до тех пор, пока не начались тесты с имитатором РЭБ-помех. Выяснилось, что контроллер питания не успевал отрабатывать скачки при переключении режимов модуляции.

Именно тогда пришло понимание: цифровая процессорная плата для систем защиты — это не просто сборка компонентов. Каждый разъём, каждый DC-DC преобразователь должны рассчитываться с учётом электромагнитной совместимости с другими модулями стойки. Кстати, у ООО Чэнду Битэ Чжиань Технологии в текущей линейке как раз удачное решение — плата с раздельными доменами питания для ЦАП и FPGA.

Сейчас вспоминаю, как в ранних версиях мы пытались экономить на тактовых генераторах. Ставили обычные кварцы вместо термостатированных OCXO — и потом месяцами ловили фазовые дрожания в каналах синхронизации. Горький опыт, но он позволил сформулировать принцип: в системах электронных контрмер цифровая процессорная плата должна рассматриваться как часть единого временного контура.

Проблемы интеграции с оборудованием синхронизации

Особенно сложно приходится при стыковке с магистральными устройствами синхронизации. Казалось бы — подал PPS, подключил 10 MHz — и работай. Но когда в цепи появляются цифровые процессорные платы с их импульсными помехами, фазовые шумы возрастают катастрофически.

Один из наших инженеров предложил гениально простое решение: развязывать земляные плоскости через ферритовые кольца. Сработало, но пришлось перекладывать 4-слойную печатную плату — вышла неделя задержки по проекту. Такие мелочи никогда не учитываются в теоретических статьях.

Кстати, на сайте https://www.cdbtzakj.ru есть технические заметки по этому поводу — они как раз описывают аналогичный кейс для оконечных устройств синхронизации. Рекомендую посмотреть, если столкнётесь с подобной проблемой.

Нюансы проектирования под российские стандарты

Многие забывают, что цифровая процессорная плата должна соответствовать не только техническим требованиям, но и нормам сертификации. В 2020-м мы получили претензию от заказчика: плата прошла все испытания, но не сертифицирована для работы в системах защиты границ.

Оказалось, проблема в использовании импортных DC-DC преобразователей — их документация не содержала необходимых деклараций соответствия. Пришлось экстренно искать замену среди российских аналогов, хотя по КПД они уступали на 15%.

Сейчас ООО BISEC Технологии ведёт работу по локализации именно в этом направлении — разрабатывают платы с учётом требований отечественных стандартов. Думаю, это правильный вектор, особенно для госзаказчиков.

Реальные кейсы отказов и их анализ

Самый показательный случай был на испытаниях в Астрахани: три цифровые процессорные платы вышли из строя одновременно при температуре +53°C. Расследование показало — производитель чипов памяти занизил тепловые характеристики в даташите.

Пришлось разрабатывать систему принудительного охлаждения с датчиками температуры прямо на кристалле FPGA. Интересно, что китайские коллеги из ООО Чэнду Битэ Чжиань Технологии столкнулись с аналогичной проблемой — их инженеры делились опытом на отраслевой конференции в Новосибирске.

Сейчас мы всегда тестируем платы в термокамере, имитируя не только штатные условия, но и пиковые нагрузки. Это добавило две недели к циклу испытаний, зато сократило процент отказов на 40%.

Перспективы развития процессорных плат для систем РЭБ

Смотрю на новые разработки — те же платы от BISEC Технологии с поддержкой Optical Flow — и понимаю: будущее за гибридными архитектурами. Чистая FPGA уже не справляется с задачами анализа спектра в реальном времени, нужны специализированные сопроцессоры.

Но здесь возникает новая проблема: совместимость программных стеков. Когда у тебя на плате три разных процессорных ядра — ARM, PowerPC и кастомный DSP — отладка превращается в кошмар. Приходится писать драйверы практически с нуля для каждого проекта.

Думаю, в следующих версиях цифровая процессорная плата будет строиться по модульному принципу, где заказчик сможет сам выбирать конфигурацию вычислительных модулей. Это снизит стоимость разработки, но потребует новых стандартов межмодульного взаимодействия.

Практические советы по выбору и тестированию

Никогда не доверяйте заводским тестам полностью. Наша практика: прогонять каждую плату через 48-часовой цикл 'нагрев-охлаждение' с одновременной нагрузкой всех интерфейсов. Да, это дорого, но дешевле, чем разбираться с отказами на объекте.

Обращайте внимание на мелочи: качество пайки BGA-компонентов, маркировку разъёмов, версию прошивки. Как-то раз получили партию, где в 30% плат был установлен кварц на 25 MHz вместо 26 MHz — обнаружили только на стендовых испытаниях.

Для систем синхронизации критично проверять джиттер тактовых генераторов. Мы используем анализатор фазового шума Rohde & Schwarz FSWP — дорогое удовольствие, но без него все гарантии бессмысленны. Кстати, на https://www.cdbtzakj.ru есть неплохой материал по методикам измерений — рекомендую к изучению.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

BL-ADH2602 Оборудование разведки и нейтрализации БПЛА

BL-ADH2602 Оборудование разведки и нейтрализации БПЛА -

Комплекс разведки и противодействия БПЛА LG-ADH1601

Комплекс разведки и противодействия БПЛА LG-ADH1601 -

Одноканальная плата разведки и подавления

Одноканальная плата разведки и подавления -

BL-ADR1102 Оборудование противодействия связи БПЛА

BL-ADR1102 Оборудование противодействия связи БПЛА -

Двухместный носимый комплекс обнаружения, подавления и противодействия БПЛА SY-BDH1601

Двухместный носимый комплекс обнаружения, подавления и противодействия БПЛА SY-BDH1601 -

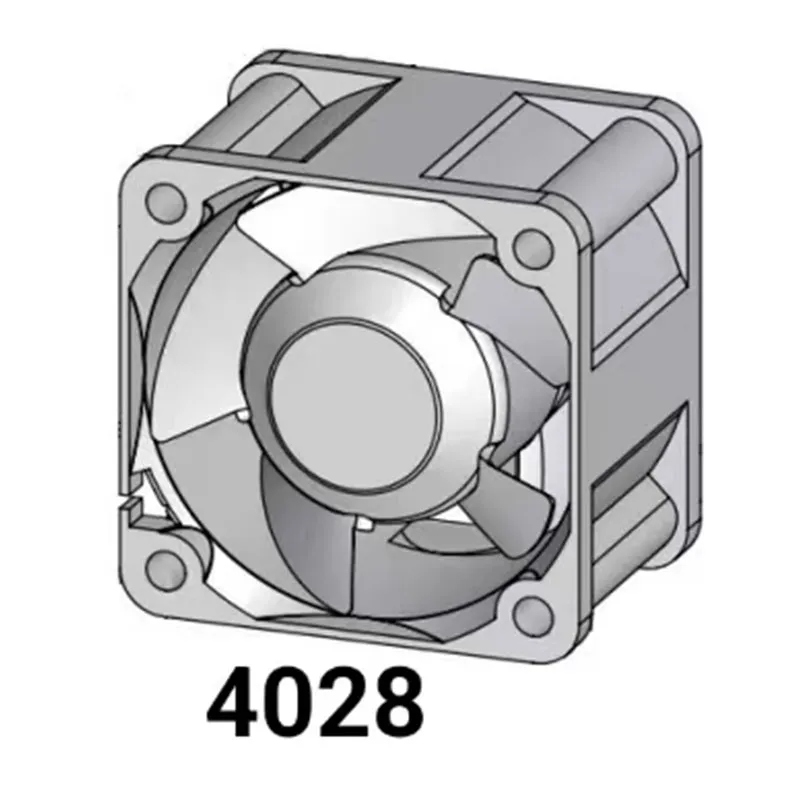

Вентилятор 4028

Вентилятор 4028 -

«Бастион» BL-ADG2001

«Бастион» BL-ADG2001 -

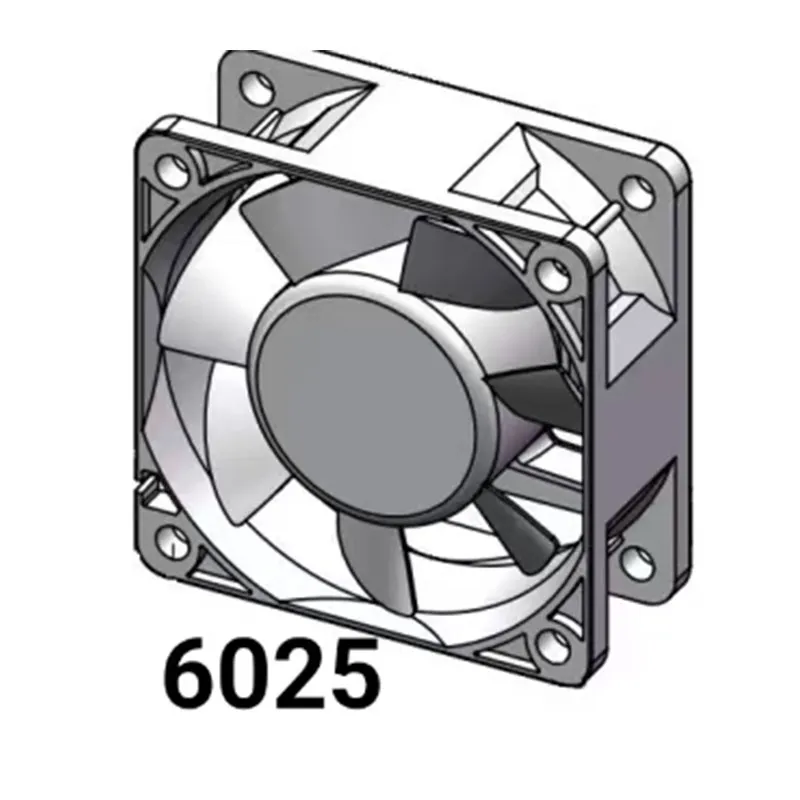

Вентилятор 6025

Вентилятор 6025 -

BL-ADG1000 Оборудование противодействия навигации БПЛА

BL-ADG1000 Оборудование противодействия навигации БПЛА -

Башенная система противодействия БПЛА

Башенная система противодействия БПЛА -

Комплекс радиотехнической разведки и пеленгации БПЛА LG-ADZ1202

Комплекс радиотехнической разведки и пеленгации БПЛА LG-ADZ1202 -

Плата обнаружения и подавления

Плата обнаружения и подавления

Связанный поиск

Связанный поиск- Китай комплекс подавления бпла cyclopter

- Китай методика борьбы с бпла

- Дешево комплекс рать для борьбы с бпла

- Автомобильный комплекс обнаружения и подавления бпла

- Zov ручной детектор обнаружения бпла

- Противодействие гоночным дронам

- Автомобильный комплекс обнаружения и подавления бпла основный покупатель

- Китай противодействие бпла противника

- Китай система противодействия бпла рэб антураж бтв

- Дешево мобильные группы по противодействию бпла